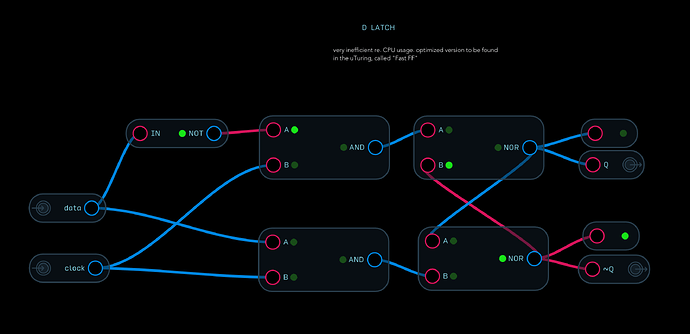

I’m trying to recreate a D-Latch, the building block of a Shift Register, without using the S&H node. I applied the exact logic diagram from wikipedia, and yes I’ve tested the truth tables of my logic gates. I think it’s working as intended, but the crucial difference between my FF and the “Fast FF” of uTuring seems to be that, in ‘Fast FF’ the data is released on clock down, and on mine it happens on clock up. I could probably find a cheat around that, but more fundamentally I wonder why a (seemingly) logically rigorous D-Latch doesn’t correctly behave in a shift register.

This is what my FF/D-Latch looks like:

Sorry for using Audulus for logic and math instead of music. It’s just too interesting

Here’s my current version of a D type flip-flop:

D Flip-FLop V3.audulus (10.8 KB)

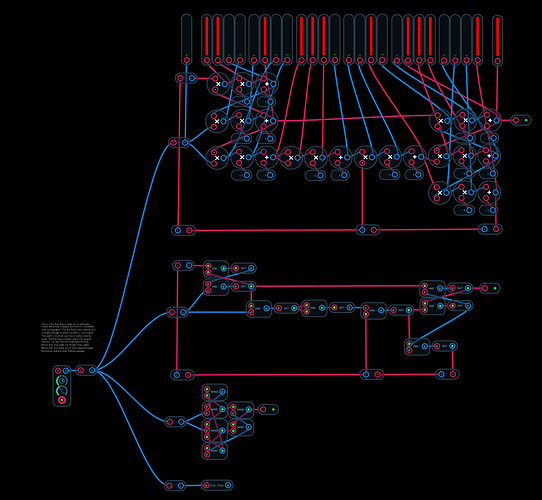

I abandoned this approach to creating a shift register because of the CPU load and chose to use a design based on the S&H node instead:

Fast Shift Register.audulus (85.8 KB)

3 Likes

I built this a long time ago just using add and mult nodes:

Arithmetic Flip-Flop.audulus (213.4 KB)

I found a different version of the D-type Flip Flop here that might work? Also it probably has to do something with the order of operations getting out of whack since you have feedback. Whenever there is feedback and it’s not acting like you want it to, it’s usually because of that. Try adding a feedback delay node at various points to see if that helps.

https://www.electronics-tutorials.ws/sequential/seq_4.html

Also check this out 4-bit computer.audulus (205.4 KB)

I forget who made this but it’s a neat little non-music thing in Audulus.

I tried making a calculator in Audulus too from the ground up (just add and mult nodes) but hit a wall somewhere and didn’t finish it.

2 Likes

![]()