Having some trouble making more dynamic sounding sequences that don’t sound like nursery rhymes. I usually work in vcv rack and the sequencers there give me an option to turn the gate on or off on any given step of the sequencer. Can anyone point me to the right direction. My apologies, been trying to come up with a good seq for days and It’s getting really frustrating.

This is one option:

https://discourse.audulus.com/t/ratcheting-sequencer-work-in-progress/1230

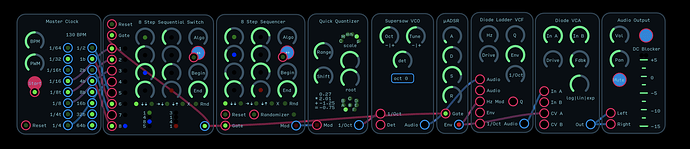

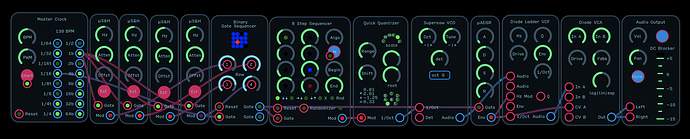

And here’s another - you basically take the output of a sequential switch that has your gate lengths in it and route it back to its input.

Different Gate Lengths Solution.audulus (621.4 KB)

If you want to introduce skips, you could just add another switch that is between the sequential switch and the gate input of the ADSR.

You can also use this module which has some cool options:

Different Gate Lengths Solution 2.audulus (574.6 KB)

There are other ways of animating sequences though - like using an LFO on the ADR periods of an envelope, or a Bernoulli Gate in between the clock and the sequencer.

Let me know if any of the above helps. In Audulus 4, we’ll just have a dang piano roll at some point, but for now, these are the two ways I can think of off the top of my head that you can do this.

PS: These new modules are available for download here, and will soon be integrated into a new update of Audulus 3.

https://discourse.audulus.com/t/audulus-3-library-reface/1455/114

Many thanks, I will give this a try!

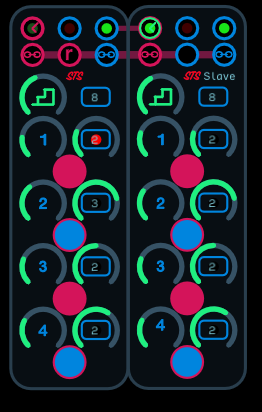

Here’s another sequencer with switchable gates. It’s part of a family of three different sequencers each of which consists of a master and a slave unit. You can chain a master and any number of slaves (including zero) to get as many steps as you need. You can set the maximum number of clocks for each unit from 0 to 48, and the number of clocks for each step. The gate output goes high at the leading edge of the first clock and falls on the trailing edge of the last, so that the gate length varies with the clock count for each step. Steps set to 0 clocks are skipped. No gate is output for the step if the gate is switched off. The three types are basic, external input and switchable gate. Here’s the switchable gate variant:

You’ll find descriptions of the I/O and controls in the file. The step value and clock count knobs for each step are intentionally switched so that you can see the clock count while adjusting it. It’s a bit confusing but better than not being able to see the number of clocks while adjusting.

uSequencers.audulus (385.1 KB)

I hope this isn’t too tangentially related. If I wanted to implement a super simple step sequencer that just has a knob for each step’s level and a toggle for each step to determine if the step fires, could simply use one of the existing clocks and a delay for each subsequent step. Basically each step passing the starting pulse to the next via the delay.

Yeah but I think that’s more resource heavy than it needs to be. To implement a step skip, you can just put a knob and multiply it by the gate signal. That way if the knob is all the way down, the step is skipped, but you can then use the knob to introduce dynamics. You’d just have to put a gate output on the sequencer.